Il prossimo campo di battaglia nell'ambito dell'elettronica dei computer sarà quello delle memorie. Dei vari mercati che caratterizzano il mondo delle componenti hardware, quello delle schedevideo è tra i più competitivi: i due maggiori produttori (Nvidia e AMD ATI) si sfidano da anni su più fronti, per offrire acceleratori grafici sempre più potenti ed energeticamente efficienti. La competizione, come accennato, sembra ora spostarsi sul campo delle memorie di lavoro: la tecnologia GDDR5 sembra essere vicina al proprio limite strutturale e tecnologico, tanto da spingere AMD a investire (anche pesantemente) su tecnologie differenti. Tra queste, la High Bandwidth Memory (abbreviata in HBM, "memoria a banda larga") sembra essere quella dotata delle maggiori potenzialità in termini di miglioramento delle prestazioni.

Problemi di memoria

Presentata a maggio 2015, la tecnologia High Bandwidth Memory prova a porre rimedio ai limiti che la GDDR5 (tecnologia utilizzata attualmente per schede video di fascia alta) comincia a mostrare. In particolare, pur offrendo prestazioni di alto livello, una scheda grafica che monta memorie GDDR5 presenta problemi di banda di comunicazione: per quanto questa possa essere larga, sembra non essere mai abbastanza.

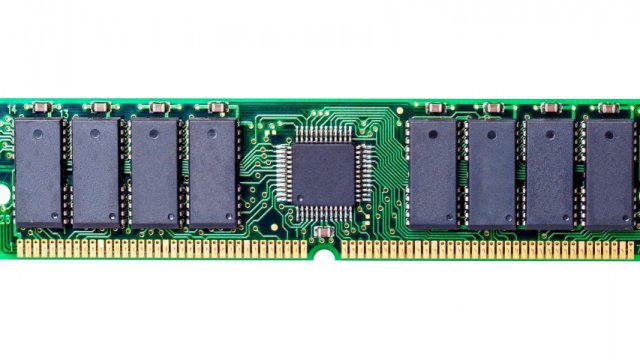

Il problema è dovuto a come i chip di memoria sono connessi con la GPU e distribuiti sulla scheda video. Le comunicazioni tra la memoria e le altri componenti della scheda grafica, infatti, sono assicurate dai pin di contatto che ogni singolo chip presenta ai quattro vertici: per aumentare la banda di comunicazione (e scambiare una maggior quantità di dati nell'unità di tempo) sarà dunque necessario aggiungere altri chip di memoria. Ciò comporta problemi logistici di varia natura per la scheda video.

I chip, infatti, dovranno essere distribuiti uno vicino all'altro intorno alla GPU, così da poter essere collegati in serie. Una sorta di formazione urbanistica decentrata, nella quale l'acceleratore grafico rappresenta il centro cittadino, mentre i blocchi di memoria possono essere comparati a quartieri e sobborghi periferici. Oltre a occupare molto spazio, una tale distribuzione logistica porta con sé altri limiti: saranno necessari più circuiti stampati sulla scheda video affinché tutti i chip di memoria possano essere collegati con la GPU. Ciò comporta anche un maggior dispendio energetico: per garantire la stessa larghezza di banda sull'intera percorrenza, sarà necessario alimentare il circuito con un voltaggio maggiore.

Ciò limita notevolmente le possibilità di ulteriore sviluppo della memoria GDRR5: difficilmente sarà possibile realizzare chip di memoria più piccoli degli attuali (così come ci ricorda la celebre legge di Moore), così da rendere energeticamente ed economicamente inefficiente questa tecnologia.

Come funziona la HBM

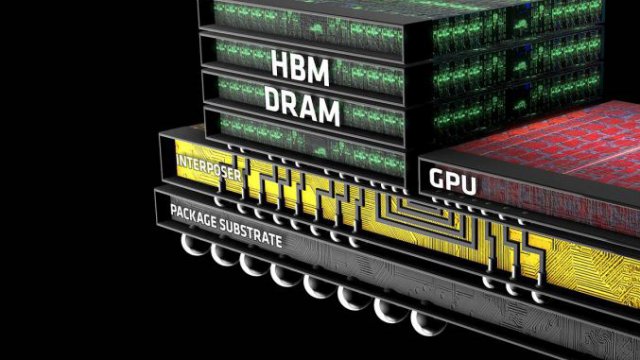

La soluzione proposta da AMD potrebbe essere considerata una sorta di rivoluzione del settore: dalla configurazione attuale con connessioni in serie, la casa canadese propone di disporre i chip di memoria l'uno sull'altro, collegandoli in parallelo e andando a formare una piccola torre. Inoltre, anziché puntare tutto su una serie di chip ad altissime prestazioni (con frequenze di lavoro da 7 gigabit al secondo), affiancati da un bus di comunicazione relativamente poco potente (qualche centinaio di bit di capienza), la High Bandwidth Memory riduce la frequenza di lavoro delle memorie (portandola ad 1 gigabit al secondo) concentrandosi invece nell'aumentare la grandezza del bus (capace di contenere fino a 4096 bit).

In questo modo, la larghezza di banda complessiva di un chip di memoria HBM supera agevolmente i 100 gigabit al secondo, mentre in un banco di memoria GDRR5 si ferma a poco meno di 30 gigabit al secondo.

Quando il gioco si fa duro

Com'è facile immaginare, un'operazione del genere è molto più semplice da pensare e descrivere che da mettere in atto. In un banco HBM, i chip di memoria disposti in verticale sono connessi tra loro tramite micro-fori applicati alle estremità del banco (chiamati through-silicon vias o TSVs) e successivamente collegati con la GPU. Ciò consente di accorciare le tracce e i percorsi seguiti dagli impulsi elettronici (e quindi dai bit e dai dati), riducendo di conseguenza il voltaggio necessario per alimentare l'intero circuito.

Si ottiene così una memoria più efficiente dal punto di vista energetico, ma di difficile realizzazione pratica: un modulo HBM ha bisogno di migliaia di tracce microscopiche da realizzare su uno spazio (quasi) infinitesimale. Basta il minimo errore di allineamento, insomma, per rendere inutilizzabile l'intero sistema.

Arriva l'Interposer

Affinché il chip di memoria possa funzionare alla perfezione si dimostra quindi necessario aggiungere un ulteriore elemento hardware, capace di gestire i flussi di comunicazione tra GPU e memoria grafica.

Ed è a questo punto che entra in gioco l'interposer, un chip di silicone capace di gestire bus di comunicazione molto ampi e, allo stesso tempo, accorciare ulteriormente la distanza tra il Die logico della GPU e la memoria HBM.